8.15 基于VHDL硬件描述语言的基带码发生器程序设计与仿真

见随书所附光盘中文件:8.15 基带码发生器VHDL程序与仿真。

1.常用基带码发生器程序

--文件名:HS_UJDM

--功能:基于VHDL硬件描述语言,产生常用基带码

--最后修改日期:2004.3.27

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity HS_UJDM is

Port (clk : in std_logic; --系统时钟

Start : in std_logic; --始能信号

dat : in std_logic_vector(15 downto 0); --二进制数据输入端

NRZ : out std_logic; --非归零信号输出端

DRZ : out std_logic; --单极性归零信号输出端

SRZ : out std_logic_vector(1 downto 0); --双极性归零信号输出端

AMI : out std_logic_vector(1 downto 0); --交替极性信号输出端

CFM : out std_logic; --差分信号输出端

CMI : out std_logic; --编码信号反转码信号输出端

FXM : out std_logic); --分相码(曼彻斯特码)信号输出端

end HS_UJDM;

architecture Behavioral of HS_UJDM is

begin

process(clk,start)

variable latch_dat : std_logic_vector(15 downto 0); --十六位二进制信号锁存器

variable latch_sig : std_logic; --高位信号锁存器

variable latch_cfm : std_logic; --差分码信号寄存器

variable latch_cnt : std_logic; --基带码同步信号

variable count_fri : integer range 0 to 8; --分频计数器(码宽定义)

variable count_mov : integer range 0 to 16; --移位计数器

begin

if start='0' then latch_cnt:='0'; --异步复位

latch_cfm:='0'; latch_sig:='0';

count_fri:=7;count_mov:=16; --异步置位

latch_dat:="0000000000000000";

elsif rising_edge(clk) then count_fri:=count_fri+1; --分频计数器+1

if count_fri=8 then count_fri:=0; --计数到8

if count_mov<16 then count_mov:=count_mov+1; --移位计数器+1

latch_sig:=latch_dat(15); --二进制码高位移入latch_sig中

latch_dat:=latch_dat(14 downto 0)&'0'; --二进制数据向高位移动一位,低位补零

else latch_dat:=dat;count_mov:=0; --载入下一轮将发送的数据

latch_cfm:='0';latch_sig:='0';latch_cnt:='0'; --寄存器复位

end if;

if latch_sig='1' then latch_cfm:=not(latch_cfm); --差分码信号寄存器中信号取反

end if;

end if;

if count_fri<4 then latch_cnt:='1'; --基带码同步信号的占空比调节

else latch_cnt:='0';

end if;

end if;

--码形转换部分

NRZ<=latch_sig; --非归零码信号

DRZ<=latch_sig and latch_cnt; --单极性归零码信号

SRZ(0)<=latch_cnt; --双极性归零码信号

SRZ(1)<=not(latch_sig); --SRZ(1)=‘1’表示负极性

AMI(0)<=latch_sig and latch_cnt; --极性交替码信号

AMI(1)<=not(latch_cfm); --AMI(1)=‘1’表示负极性

CFM<=latch_cfm; --差分码信号

FXM<=latch_cnt xnor latch_sig; --分相码信号

if latch_sig='1' then CMI<=latch_cfm; --编码信号反转码

else CMI<=not(latch_cnt);

end if;

end process;

end Behavioral;

2.常用基带码发生器程序仿真

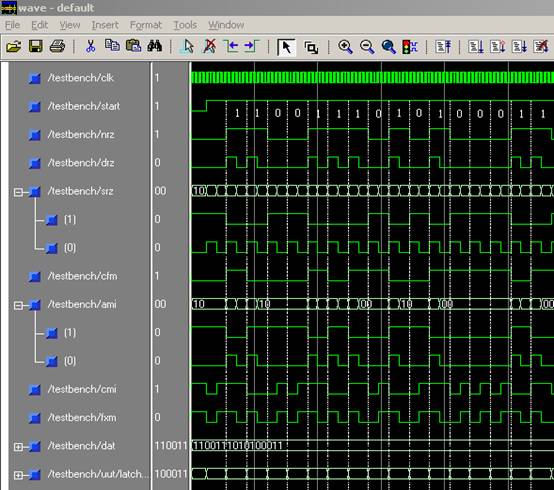

常用基带码时序仿真图如图8.15.7所示:

(a)局部放大图

(b)全局仿真图

图8.15.7常用基带码时序仿真图

如图所示当start到来一个高电平时,则启动二进制码与NRZ码转换。在第一个同步信号到来时寄存器载入外部十六位数据,之后每来一个同步信号则将寄存器中最高位送出,码形转换器开始工作,将转换后的码形由相应的端口输出,与此同时十六位寄存器中的低十五位数据向高位移动一位并且低位补零。