0 引言

在许多嵌入式系统的实际应用中,需要扩展FP-GA(现场可编程门阵列)模块,将CPU实现有困难或实现效率低的部分用FPGA实现,如数字信号处理、硬件数字滤波器、各种算法等,或者利用FPGA来扩展I/O接口,如实现多路PWM(脉宽调制)输出、实现PCI接口扩展等。通过合理的系统软硬件功能划分,结合优秀高效的FPGA设计,整个嵌入式系统的效率和功能可以得到最大限度的提高。

在电机控制等许多应用场合,需要产生多路频率和脉冲宽度可调的PWM波形。本文用Altera公司FPGA产品开发工具QuartusⅡ,设计了6路PWM输出接口,并下载到FPGA,实现与CPU的协同工作。

1 FPGA概述

PLD(可编程逻辑器件)可分为SPLD(简单可编程逻辑器件),CPLD(复杂可编程逻辑器件)和FPGA,其实它们只是在起初有一些差别,现在的区别已经比较模糊了,PLD可统称为FPGA。目前世界上有十几家生产CPLD/FPGA的公司,知名度较大的有Altera,Xil-inx,Lattice,Actel等,其中Altera和Xilinx占有了60%以上的市场份额。

Altera公司是最大PLD供应商之一,20世纪90年代以后发展很快。主要产品有:MAX3000/7000、FLEX10K、APEX20K、ACEX1K、StratiX、Cyclone等。开发软件为MaxplusⅡ和QuartusⅡ。普遍认为其开发工具MaxplusⅡ和QuartusⅡ是最成功的FPGA开发平台之一,配合使用Altera公司提供的免费OEM HDL综合工具可以达到较高的效率。

对于系统设计人员来说,FPGA是一种可以自己编程的芯片。它从芯片制造厂商那里出来时是内部没有连线的。用户可以进行设计输人(电路图输入、状态机输入或者HDL输入);然后进行仿真和验证;接着用一些专用软件(如Synopsys FPGA-Compiler、Synplici-ty Synplify、Examplar Leonardo等)进行逻辑综合;最后使用各个FPGA厂商自身的后端实现的软件(如Al-tera Quartus、Xilinx ISE等)进行布局布线,生成一个配置所需设计的电路连线关系的二进制流文件,通过一根连接PC机和FPGA芯片的下载线,将配置文件下载到芯片中。

本文以使用QuartusⅡ软件设计PWM为例,介绍FPGA设计的流程,它包括设计输入、约束输入、逻辑综合、逻辑验证(综合后仿真)、布局布线(器件实现)和器件验证(版图后仿真)等几部分。

2 多路PWM的设计实现

PWM技术最初是在无线电技术中用于信号的调制,后来在电机调速中得到了很好的应用。在直流伺服控制系统中,通过专用集成芯片或中小规模数字集成电路构成的传统PWM控制电路往往存在电路设计复杂、体积大、抗干扰能力差以及设计困难、设计周期长等缺点,因此PWM控制电路的模块化、集成化已成为发展趋势。它不仅可以使系统体积减小、重量减轻且功耗降低,同时可使系统的可靠性大大提高。随着电子技术的发展,特别是ASIC(专用集成电路)设计技术的日趋完善,数字化的EDA(电子设计自动化)工具给电子设计带来了巨大变革,在电机控制等许多应用场合,需要产生多路频率和脉冲宽度可调的PWM波形,这可通过FPGA丰富的硬件资源和可以配置I/O引脚来实现。嵌入式系统中FPGA的应用设计关键是系统软硬件功能的划分。

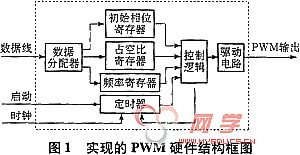

图1是实现的3路PWM硬件结构框图。CPU通过数据线向FPGA写入定时常数控制PWM的频率、初始相位和占空比,并通过外部启动信号控制PWM的启动。

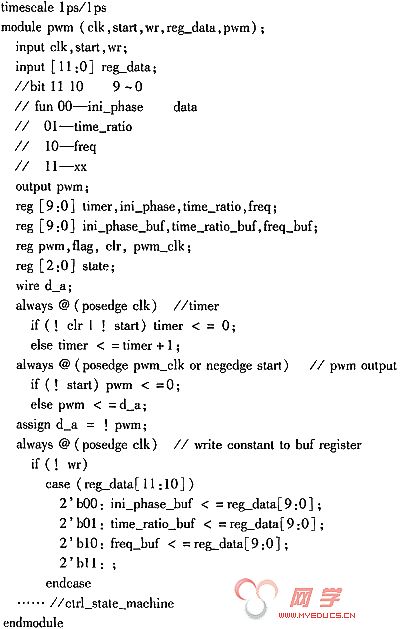

根据图1,写出实现相应功能的Verilog程序描述。部分源程序如下:

图2显示了QuartusⅡ中新建一个项目/文件时可选的设计输入(在Software Files和Other Files标签中还要其他设计输入方法选择),该窗口从菜单"File"→"New"打开,图中显示了"Device Design files"标签下的设计输入方法有AHDL(Altera 公司开发的HDL语言)、方块图/原理图、EDIF、Verilog和VHDL输入方法。另外在"Software Files''和"Other Files"标签下还有TCL语言、波形图等其他输入方法。

3 逻辑仿真和器件验证

行为级仿真是在HDL源代码设计完成之后,通过设计测试平台文件(激励和测试矢量)来验证设计的正确性。逻辑仿真是在逻辑综合之后,对生成的门级网表进行验证。测试平台文件与采用行为级仿真的测试平台文件,这样能够保证设计验证的一致性。并且,逻辑验证是一种理想的门级网表,不存在延时信息。器件验证也称版图后仿真,它是在FPGA实现之后,提取出门级网表和延时信息进行验证,测试平台文件与行为级一样。器件验证结果是比较接近真实硬件的结果。完全通过这3层的验证,基本上可以保证设计的结果与测试平台文件一致。

行为仿真和器件仿真也可直接在QuartusⅡ中进行,其中输入激励波形和输出观察节点在QuartusⅡ波形输入窗口进行设置,在设计通过功能仿真后,需要进一步选择器件仿真以验证设计的正确性。器件仿真时包含了所选择的对应FPGA估算延时或实际延时信息,故仿真速度较功能仿真慢很多。通过仿真可以及早发现设计中的错误,并根据具体情况进行修改,包括修改硬件实现架构、设计代码、约束条件等一个或多个方面。器件仿真通过后,则可以将设计下载到芯片,进行硬件功能验证。

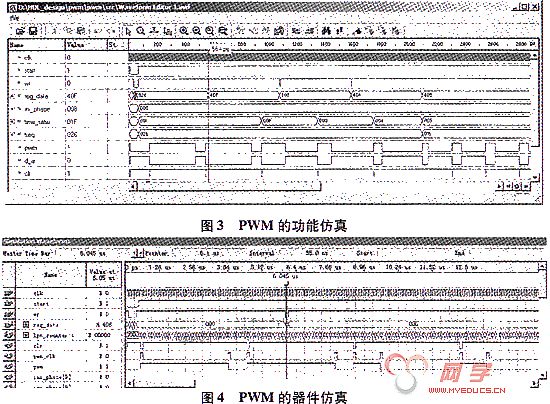

图3是对应PWM的功能仿真结果波形。从图3中可以看出,在564 ps时刻CPU向PWM写入新的控制常数后,下一个周期的PWM输出占空比立刻发生了相应改变。

图4是相应设计在QuartusⅡ下编译通过后进行器件仿真的波形,由图4可见,其时序功能正确。通过器件下载编程方法下载到相应的FPGA,就可以结合整个嵌入式系统进行硬件调试。

4 结束语

在FPGA开发软件中完成设计以后,软件会产生一个最终的编程文件,QuartusⅡ中是.pof或.sof。现在的FPGA基本都采用在系统编程方式,对于EEP-ROM/Flask/SRAM工艺的在系统可编程FPGA,厂家提供编程电缆,如Altera公司提供的下载电缆类型有ByteBlasterⅡ并口下载电缆、USB BlasterTMUSB口下载电缆、MasterBlaster 通信缆线(USB或RS-232端口)等,其配置方式可以有主动/被动串行配置方式、JTAG方式等。电缆一端装在计算机的相应接口上,另一端接至PCB(印制电路板)上的编程插头,它向系统板上的器件提供配置或编程数据,这就是所谓的ISP(在线系统编程)。

在电机控制等许多应用场合,需要产生多路频率和脉冲宽度可调的PWM波形,本文通过使用Altera公司FPGA产品开发工具QuartusⅡ,设计了6路PWM输出接口,并下载到FPGA,实现与CPU的协同工作。在嵌入式系统中通过FPGA扩展系统功能的设计是一种有效的方法。